수리과학, 물리학, 화학, 생명과학 분야와 이들을 기반으로 한 융&복합 분야

미래 산업 경쟁력 강화의 근간이 되는 소재 및 ICT 분야

과제 & 연구자

과제 & 연구자

큰 꿈을 향한 무한탐구의 연구열정,

삼성미래기술육성사업이 응원하며 함께 하겠습니다.

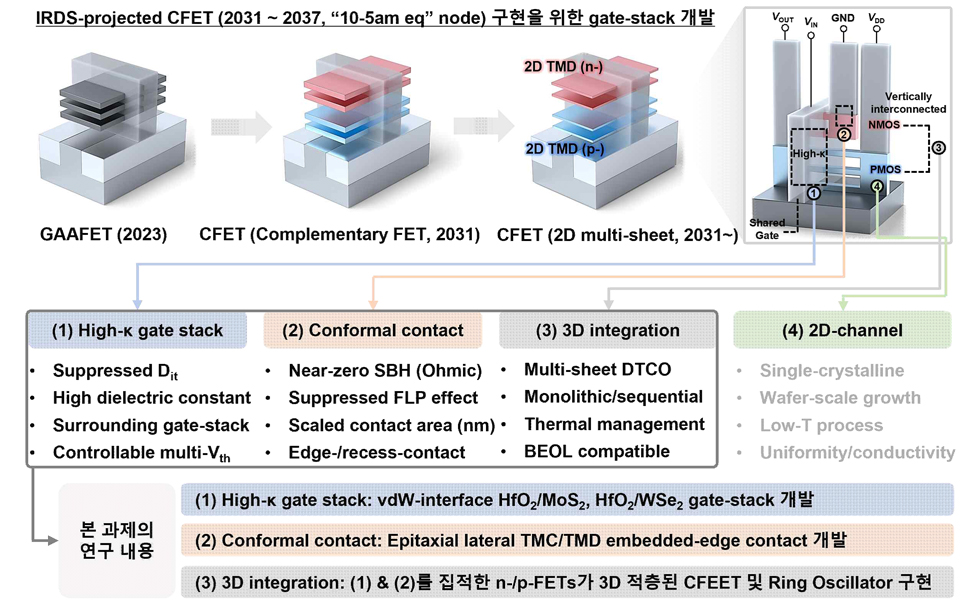

반데르발스 계면 및 에픽텍시얼 접합 구조의 이차원 반도체 CFET

본 과제는 IRDS (International Roadmap for Devices and Systems) “2031~2037, 10~5am eq logic node”의 multi-sheet 기반 3D-stacked CFET에 적용 예상되는 이차원 반도체의 집적을 위한 4가지 핵심 기술, (1) high-κ gate stack-, (2) conformal contact-, (3) 3D integration-, (4) 2D-channel-technology 중 (1), (2)의 개발과 (3) 3D CFET 구현을 목표로 하는 연구입니다.

먼저, Surface dangling bond-free한 이차원 반도체의 상부에 적층된 2D-precursor만을 high-κnative oxide로 변환하여 2D-channel (n-/p- TMD) 적층 시 형성되는 vdW interface를 intact하게 유지하는 interface-terminated dielectric 집적기술을 n-/p- TMD에 개발하는 연구입니다.

이차원 반도체의 metal-semiconductor contact 문제 해결을 위해 2D-channel 측면에서 catalyst induced carbonization/nitridation에 의해 진행되는 제어 가능한 수평 방향의 선택적 탄화 기술(선행연구)을 개선하여 atomic & electronic alignment가 개선된 atomically sharp한 TMD/TMC 형태의 lateral edge-/recess-contact 형성 기술을 개발합니다.

본 과제를 통해서 향후 multi-sheet CFET 구조에 적용될 이차원 반도체의 컴팩트한 적용을 위한 범용적 신개념 high-κ, conformal contact, 3D integration 기술을 확보하고, 이를 이용한 CFET 및 Ring Oscillator를 구현함으로써, 공정*소자*회로의 통합적 설계 기술 IP의 확보 및 원천기술을 개발하고자 합니다.

본 과제는 IRDS (International Roadmap for Devices and Systems) “2031~2037, 10~5am eq logic node”의 multi-sheet 기반 3D-stacked CFET에 적용 예상되는 이차원 반도체의 집적을 위한 4가지 핵심 기술, (1) high-κ gate stack-, (2) conformal contact-, (3) 3D integration-, (4) 2D-channel-technology 중 (1), (2)의 개발과 (3) 3D CFET 구현을 목표로 하는 연구입니다. 먼저, Surface dangling bond-free한 이차원 반도체의 상부에 적층된 2D-precursor만을 high-κnative oxide로 변환하여 2D-channel (n-/p- TMD) 적층 시 형성