과제 & 연구자

큰 꿈을 향한 무한탐구의 연구열정,

삼성미래기술육성사업이 응원하며 함께 하겠습니다.

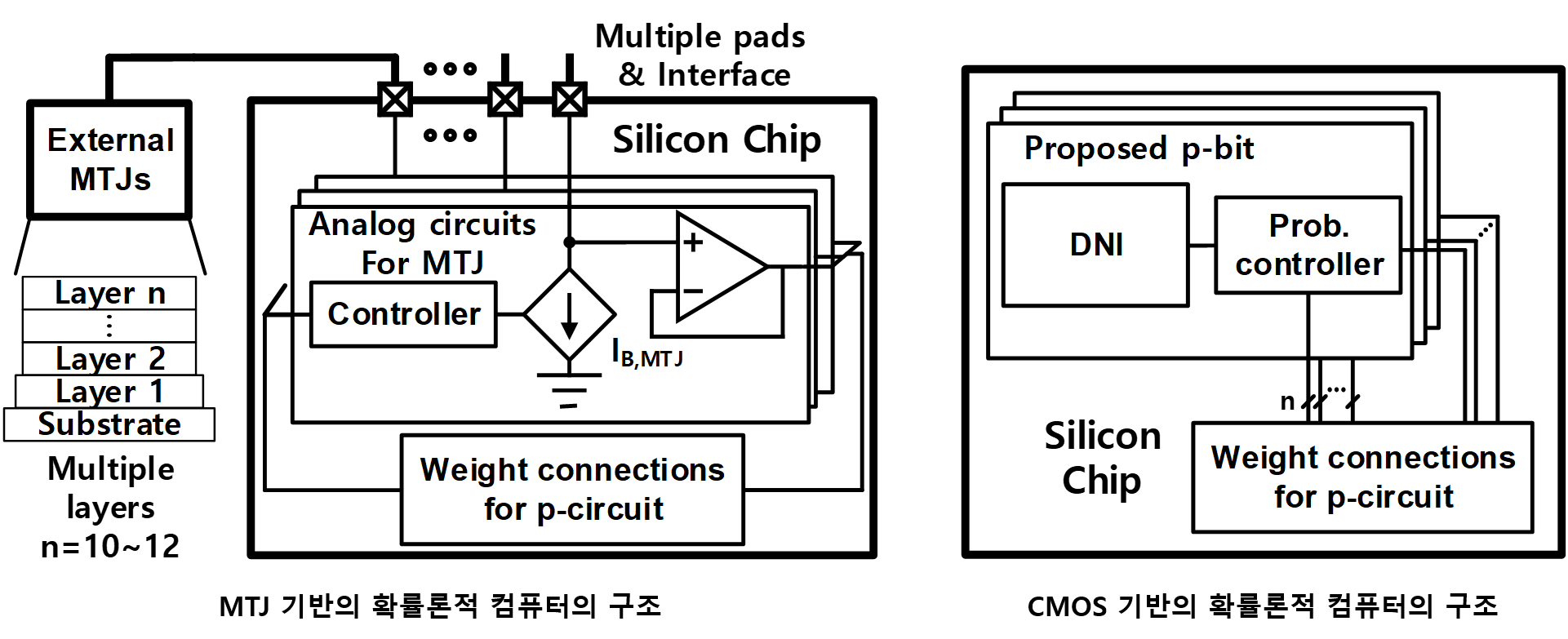

현재 널리 쓰이는 컴퓨터는 다항 시간 안에 풀기 어려운 문제 (NP problem)를 효율적으로 풀 수 없습니다. 기존 컴퓨터가 한계를 보인 이유는 결정론적 동작을 하기 때문인데, 이는 비결정론적 컴퓨팅 기술 중 하나인 확률론적 컴퓨팅이 등장하는 배경이 되었습니다. 확률론적 컴퓨터는 논리적 ‘1’이 출력될 확률이 조절되는 랜덤 소자인 확률론적 비트 (probabilistic bit, p-bit)를 연산 단위로 사용합니다. 기존에 제안된 p-bit는 MRAM에서 사용 되는 자기터널접합 (magnetic tunnel junction, MTJ)의 에너지 장벽을 낮추고, 인가 되는 바이어스 전류의 크기를 조절하여 p-bit의 논리적 ‘1’ 출력 확률을 조절 합니다. 이 방식은 MTJ의 특성을 보완하기 위한 별도의 보상 회로가 필요하고, 대규모 집적을 위한 추가적인 기술 개발이 필요합니다.

본 과제에서는 랜덤 소자를 CMOS 집적 회로로 구현해서 확률론적 컴퓨팅 기술을 실현하고 역연산 동작을 검증할 계획 입니다. CMOS 트랜지스터로 시스템을 구현할 때의 장점은 첫째로 복잡한 문제를 풀기 위해 필요한 많은 수의 p-bit을 집적하고 연결을 구성하기에 적합하다는 점 입니다. 둘째로 이미 상용화 된 CMOS 공정을 사용하므로 빠른 제품화가 가능하고, 공정 노드 축소에 따른 동작 속도 향상과 소비 전력 감소 효과를 얻을 수 있습니다.

그림 1. 두 가지 방식의 확률론적 컴퓨터의 구조

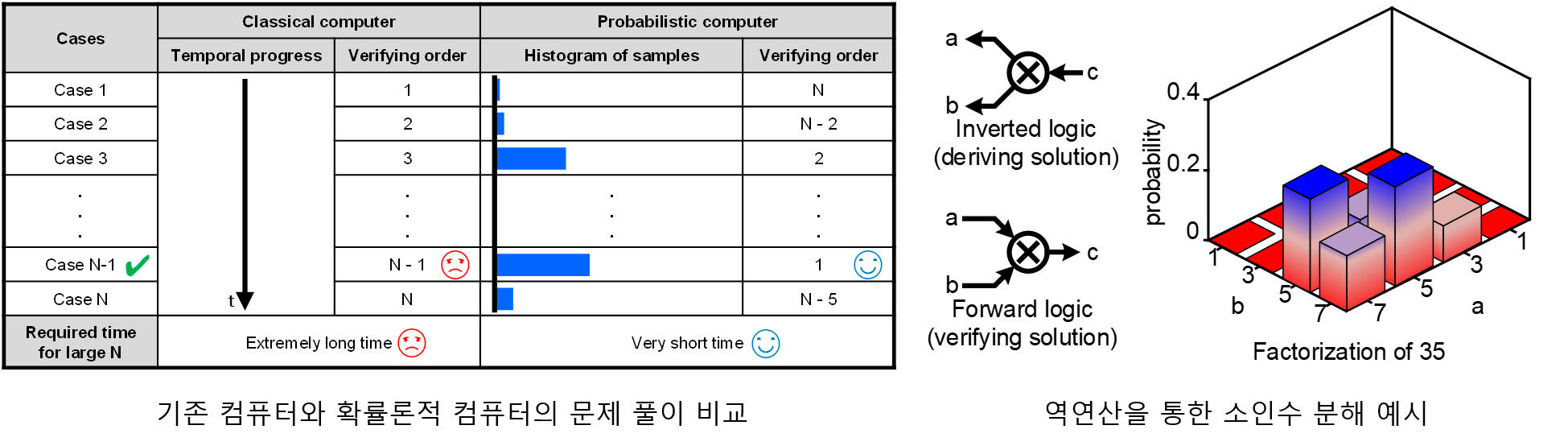

본 과제는 CMOS 기반의 확률론적 컴퓨팅 기술과 역연산 기법의 연구를 통해 다가올 차세대 컴퓨팅 시장에서 핵심 IP를 확보할 것으로 예상 됩니다. 연구의 성과물은 RSA 암호화 기술, 최적화 문제 풀이, 그리고 stochastic neural network의 하드웨어 가속기 등 다양한 컴퓨팅 환경에서 활용될 것으로 기대 됩니다.

그림 2. 확률론적 컴퓨팅의 검산 방식과 소인수 분해 결과 예시

현재 널리 쓰이는 컴퓨터는 다항 시간 안에 풀기 어려운 문제 (NP problem)를 효율적으로 풀 수 없습니다. 기존 컴퓨터가 한계를 보인 이유는 결정론적 동작을 하기 때문인데, 이는 비결정론적 컴퓨팅 기술 중 하나인 확률론적 컴퓨팅이 등장하는 배경이 되었습니다. 확률론적 컴퓨터는 논리적 ‘1’이 출력될 확률이 조절되는 랜덤 소자인 확률론적 비트 (probabilistic bit, p-bit)를 연산 단위로 사용합니다. 기존에 제안된 p-bit는 MRAM에서 사용 되는 자기터널접합 (magnetic tunnel junction, MTJ)의 에너지 장벽을 낮추고, 인가 되는 바이어스 전류의 크기를 조절하여 p-bit의 논리적 ‘1’ 출력 확률을 조절 합니다. 이 방식은 MTJ의 특성을 보완하기 위한 별도의 보상 회로가 필요하고, 대규모 집적